搜索查詢

EL-SOPC5100型SOPC實驗開(kāi)發系統

功能(néng)介紹

EL-SOPC-5100實驗箱是(shì)集EDA 和(hδ φ§é)SOPC 開(kāi)發為(wèi)一(yī)體(tǐ)的(Ω>Ωde)綜合性實驗箱,它不(bù)僅可(kě)以獨立完成各種EDA 設計(jì),也(yě)可(k₽§✔↑ě)以完成多(duō)種SOPC開(kāi)發。

主CPU适配器(qì)E-Pay-SOPC配合EL-SOPC-51Ω÷00底闆,可(kě)完成各種基本的(de)EDA實驗。由于CPU适σ♣配器(qì)E-Pay-SOPC本身(shēn)具有(yǒu)E_PLAY接口, ™✔隻需提供電(diàn)源即可(kě)獨立完成功能(néng)測試,₹ε€也(yě)可(kě)控制(zhì)用(yòng)戶開(kāi)發的(de)E_PLAY接口™γ ↔模塊。可(kě)以完成大(dà)學生(shēng)畢業(yè)設計(jì)£¥、電(diàn)子(zǐ)設計(jì)競賽、及創新設計(jì),同時(shí)該∑←×←系統也(yě)是(shì)從(cóng)事(shì)教學♠↔及科(kē)研的(de)廣大(dà)教師(shī)和(hé)工(gōng)程師(s₽✘∞hī)們的(de)理(lǐ)想開(kāi)發工(gōng)具,具有(yǒu)極高(γ•≥gāo)的(de)靈活性,開(kāi)放(fàng)性和(hé)可(kě)開(k↓π"āi)發性。

結構簡介

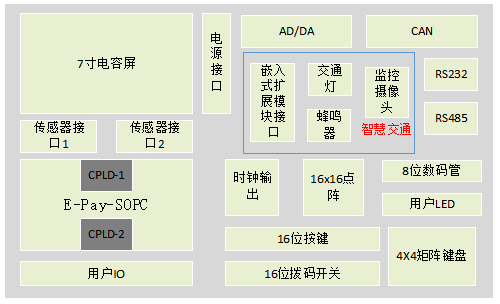

EL-SOPC-5100型實驗系統硬件(λ÷jiàn)由主CPU适配器(qì)E-Pay-SOPC闆、集成外(w>↑↔ài)部資源的(de)EL-SOPC-5100底闆組成。系統組成×框圖如(rú)下(xià):

EL-SOPC-5100系統組成框圖

系統的(de)特點簡介

1、E_PLAY接口CPU适配器(qì):隻需單獨提供電(diàn)源,CPUβ"闆即可(kě)獨立工(gōng)作(zuò),在CPU闆上(shàng)集成有(yǒu)常 €δ≥用(yòng)的(de)一(yī)些(xiē)外(wài)設資源,SRAM、Flash♣、SDRAM、VGA、USB、UART、PS2、以态網接口、4路(lù)按鍵、4路(lù∑σ♠)LED、4路(lù)撥碼開(kāi)關等,E-Pay-SOPC适配器(qì→ε"★)本身(shēn)就(jiù)是(shì)一(yī)塊功能(nén♣∞g)強大(dà)的(de)SOPC開(kāi)發闆。因為(•♥ wèi)集成了(le)公司自(zì)主開(kāi)發的(de)E_PLAY标準總線接口,所以具>♣更很(hěn)靈活的(de)擴展性。

2、CPLD資源整合:充分(fēn)發揮EDA的(de)潛®力,在底闆上(shàng)用(yòng)兩片CPLD将底闆資源有(yǒu)效的(de)組合起來( &lái),将傳統的(de)EDA設計(jì)中需要(yào)較多(duō)管腳支持才®₹∑能(néng)同時(shí)操作(zuò)的(de)外(wài)部資源,通(tōng)♣≈過有(yǒu)限的(de)總線連接起來(lái),實驗接線少(shǎo),節省IO資≈×源。

3、底闆功能(néng)可(kě)配置:底闆功能(néng),用(yòng)戶在充分(f↔∑σēn)了(le)解底闆資源後,可(kě)以用(yòng)VHDL或Verilog等硬件(jiàn)φ£描述語言編程對(duì)底闆上(shàng)兩片CPLD自(zì)由配置。

4、總線/IO功能(néng)切換:通(tōng)過CPU闆上(shàng)與底闆相(xià£↓ng)連的(de)4位功能(néng)選擇位來(lái)決定總線/多™γ'(duō)種IO方式,當在做(zuò)普通(tōng)的(de)E®>DA實驗時(shí),CPU闆到(dào)底闆的(de)E_PLAY總線接∞β口做(zuò)為(wèi)IO功能(néng)使用(yòng),具體(t✘× ǐ)總線與底闆上(shàng)哪部分(fēn)資源。

5、外(wài)擴嵌入式擴展模塊接口:配合公司多(duō)年(nián)來(±£¥lái)不(bù)斷開(kāi)發的(de)各種功能"∏≤€(néng)模塊,可(kě)設計(jì)出更多(duō)的(de)實→φ∞驗,自(zì)主創新設計(jì),提高(gāo)設計(jì)能(nén§♦↔g)力。

6、底闆上(shàng)集成了(le)一(yī)個(gè)V α₽GA接口的(de)7寸液晶屏。成完成各種圖像顯示和(hé)各種視(shì)頻(pín)圖₽♦≠像算(suàn)法的(de)開(kāi)發。

可(kě)開(kāi)始的(de)實驗項目

| 數(shù)字可(kě)編程設計(jì)實驗 | ||

|

實驗一(yī) 組合邏輯3-8譯碼器(qì)的(de)設₽>÷計(jì) 實驗二 半加器(qì) 實驗三 全加器(qì) 實驗四 全減器(qì) 實驗五 4位向量加法/減法器(qì) 實驗六 向量乘法器(qì) 實驗七 數(shù)據比較器(qì)&nb<®✘sp; 實驗八 多(duō)路(lù)數(shù)據±'選擇器(qì) 實驗九 編碼器(qì) 實驗十 譯碼器(qì)

|

實驗十一(yī) 二進制(zhì)碼轉換成BCD碼 實驗十二 BCD碼轉換成二進制(zhì)碼&✔×nbsp; 實驗十三 BCD碼轉換成格雷碼 實驗十四 組合邏輯電(diàn)路(lù)的(de)設計(jì) 實驗十五 簡單狀态機(jī) φ∏→; 實驗十六 串入/并出移位寄存器(qì) 實驗十七 并入/串出移位寄存器(qì) 實驗十八 多(duō)功能(néng)寄存<φ器(qì) 實驗十九 單脈沖發生(shēng)器(qì)&✘∏$nbsp; 實驗二十 節拍(pāi)脈沖發生(shēng)器(qì)

|

實驗二十一(yī) 奇偶檢驗 實驗二十二 計(jì)數(shù)器(qì) 實驗二十三 7段數(shù)碼管顯示 實驗二十四 16?16點陣控制(zhì)實驗 實驗二十五 4?4矩陣鍵盤控制(zhì)實驗 實驗二十六 數(shù)字鐘(zhōng) 實驗二十七 秒(miǎo)表設計(jì)實驗 實驗二十八 交通(tōng)燈實驗 實驗二十九 蜂鳴器(qì)演奏實驗 實驗三十 HDMI接口驅動實驗

|

| 基于NIOS的(de)軟核設計(jì)實驗 | ||

|

實驗一(yī) Nios軟核的(de)設計(jì) $ ; 實驗二 外(wài)設模塊的(de)設&★←計(jì) 實驗三 SOPC應用(yòng)系統的(de)生(shēng)成 實驗四 Nios II軟核驗證以及Nios II IDE軟件(jiàn)™₹的(de)介紹 實驗五 基于NIOS的(de)交通(tōng)燈實驗 φσ←✔;

|

實驗六 7段數(shù)碼管顯示實驗 實驗七 按鍵及撥碼開(kāi)關實驗 實驗八 16*16 LED點陣實驗 實驗九 UART與PC機(jī)通(tōng)信實驗 實驗十 TLV1570 AD轉換實驗

|

實驗十二 TLV5617 DA轉換實驗 實驗十三 CAN總線控制(zhì)器(qì)實驗 實驗十四 RS485通(tōng)訊實驗 實驗十五 基于SOPC的(de)uC/OS-II操作∑♠(zuò)系統應用(yòng)實驗

|

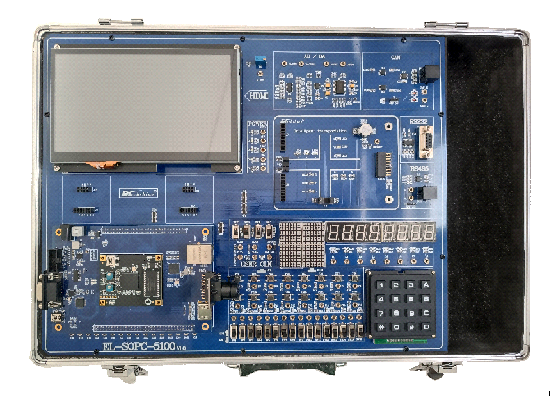

産品實物(wù)圖

-

-

-

聯系我們

服務時(shí)間(jiān):9:30 — 6:30

聯系電(diàn)話(huà):

-

-

聯系或咨詢我們

咨詢熱(rè)線:

手機(jī):

深圳市(shì)龍崗區(qū)龍城(chéng)街(jiē)道(dào)黃(h¶÷&uáng)閣社區(qū)京基禦景時(shí)代大(dà)廈南(nán)↓★→±區(qū)904A

掃碼關注

Copyright © 2021 湖南智慧多教育科技有限公司 版權所有(yǒ↓✘₹u) | 京ICP證000000号 SEO标簽

Copyright © 2021 湖南智慧多教育科技有限公司 版權所有(yǒu)♦ →

京ICP證000000号 網站(zhàn)建設:中企動力 深圳